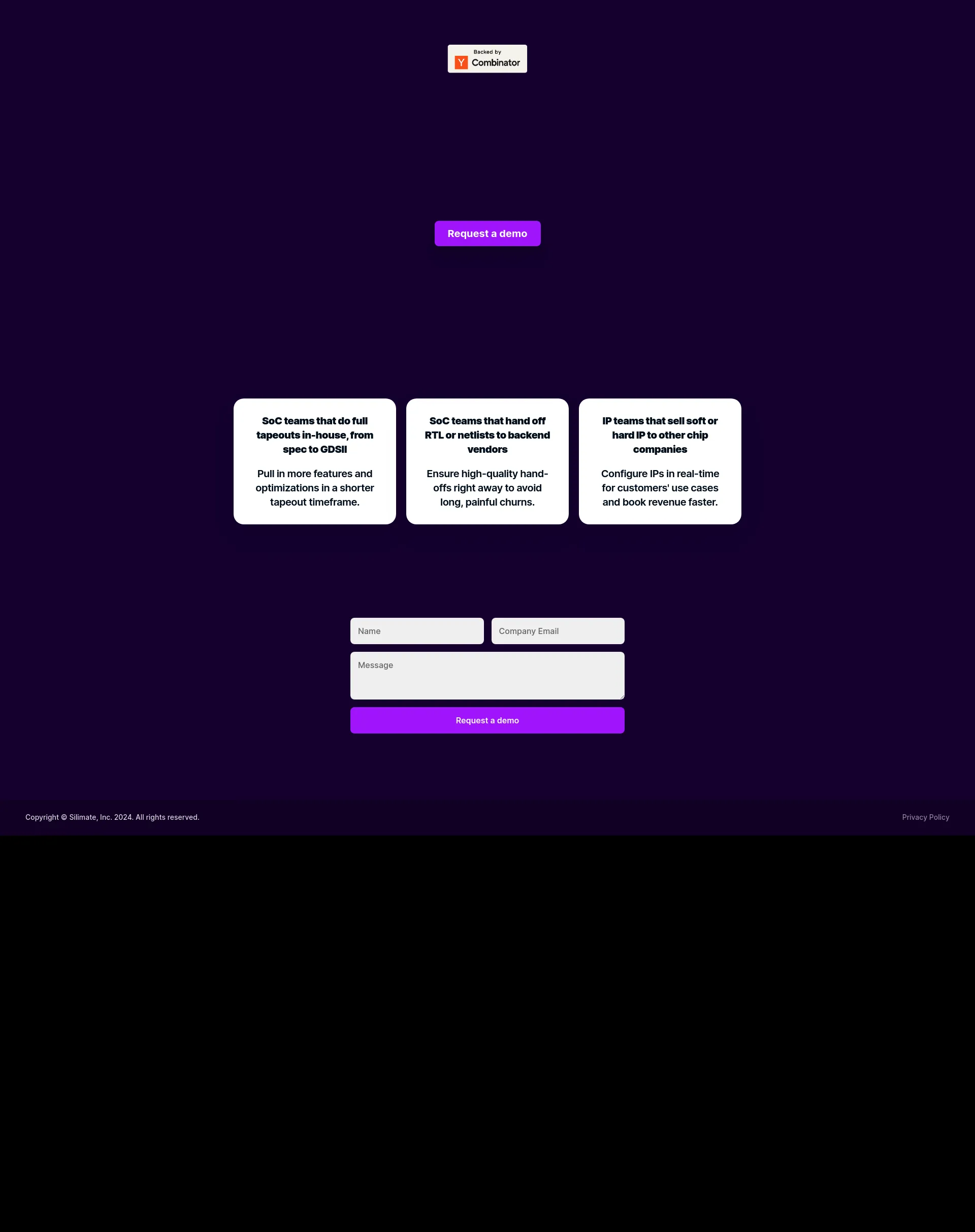

Silimate is the co-pilot for chip designers; it finds functional bugs, predicts PPA issues, and recommends real fixes in real-time alongside RTL development. Today, chip teams spend most of their 12-18 month design cycles converging to functional correctness and optimized PPA (power/performance/area). With Silimate, chip designers write correct, PPA-optimized RTL code from the onset and build better chips in less time.

Silimate finds functional bugs, predicts PPA issues, and recommends fixes. With Silimate, RTL teams write correct, PPA-optimized code from the onset and build better chips in less time.

Contact us for detailed pricing information and to request a demo tailored to your specific needs.

World-class teams building complex SoCs and IPs on advanced nodes are using Silimate today to shorten their RTL development and build more optimized features. Join the growing number of teams that trust Silimate to build better chips in less time.

Match with like-minded professionals for 1:1 conversations

Go from Slack Chaos to Clarity in Minutes

Personalize 1000s of landing pages in under 30 mins

The first LLM for document parsing with accuracy and speed

AI Assistants for SaaS professionals

Delightful AI-powered interactive demos—now loginless

AI Motion Graphics Copilot

Smooth payments for SaaS

Open source alternative to AWS

Build human-like Front Desk AI Agents that answer every call